## VERIFICATION OF A 65NM CMOS IC FOR VARIOUS APPLICATIONS (NEUTRINO DETECTION, HIGH ENERGY PHYSICS, ETC.)

18TH APRIL 2018 | CHRISTIAN ROTH

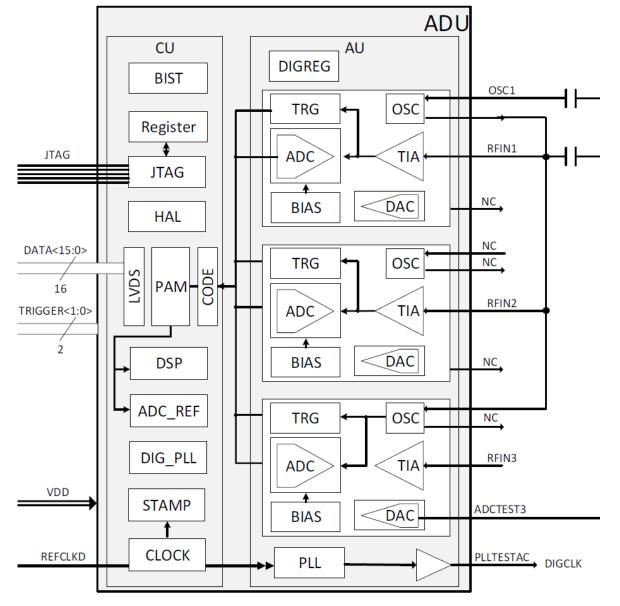

#### **VULCAN CHIP OVERVIEW**

- The Vulcan Chip

- Highly linear, fully integrated circuit Vulcan

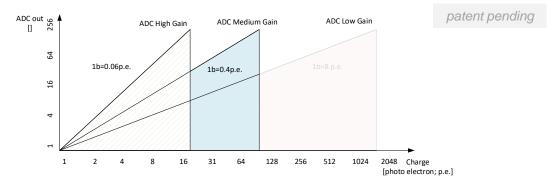

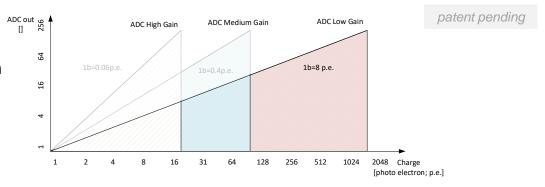

- Sampling ADC with approx. 80 dB linearity (3 signal chains with 3 different gains)

- No external components required

- On-chip clock generation from ref. clock

- Precise signal reconstruction

- No analog delay line (reducing noise & distortion)

- Control loop to suppress DC variations

- Optional overshoot compensation

- Further key parameters of Vulcan:

- ADC with 9.5 bit (3x 8 bit), 1 Gsample/s

- Transimpedance Amplifier (TIA)

Input impedance of < 10 Ohm</li>

- Power consumption ~ 1.2 Watt

# **Digital**

#### **VULCAN IC LAYOUT**

**Key Parameter of Vulcan**

65 nm CMOS Process

Active Area 22 mm<sup>2</sup> Power ~ 1.2 W

< 10 Ohm Input Impedance

Input Bandwidth 500 MHz

Sampling Rate 1 Gsample/s

Dynamic Range 80 dB

**ADC** Resolution 3x 8 bit

High Gain 0.06 p.e./bit Medium Gain 0.4 p.e./bit

Low Gain 8 p.e./bit

4.7mm

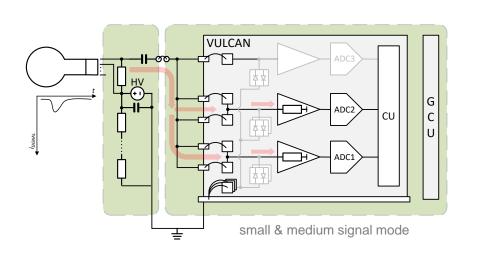

#### **VULCAN SIGNAL MODES**

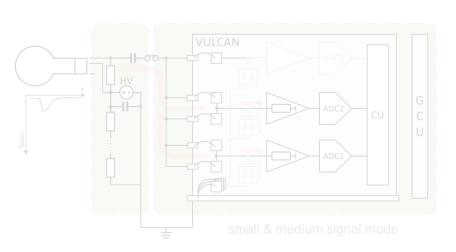

• Signal Modes – Small & Medium Signals

#### First two signal chains

- Parallel TIA input

- Programmable gains

- Combined input resistance  $R \approx 5 \Omega$

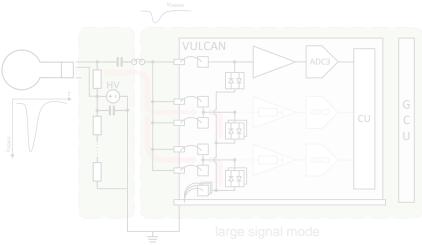

#### **VULCAN SIGNAL MODES**

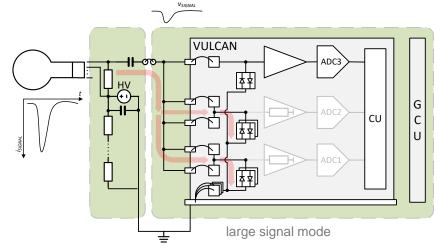

Signal Modes – Large Signals

#### Third signal chain

- Current > 20 mA

- TIA input saturates, ESD diodes open

- Voltage over diodes measured

- Combined input resistance  $R \approx 5 \Omega$

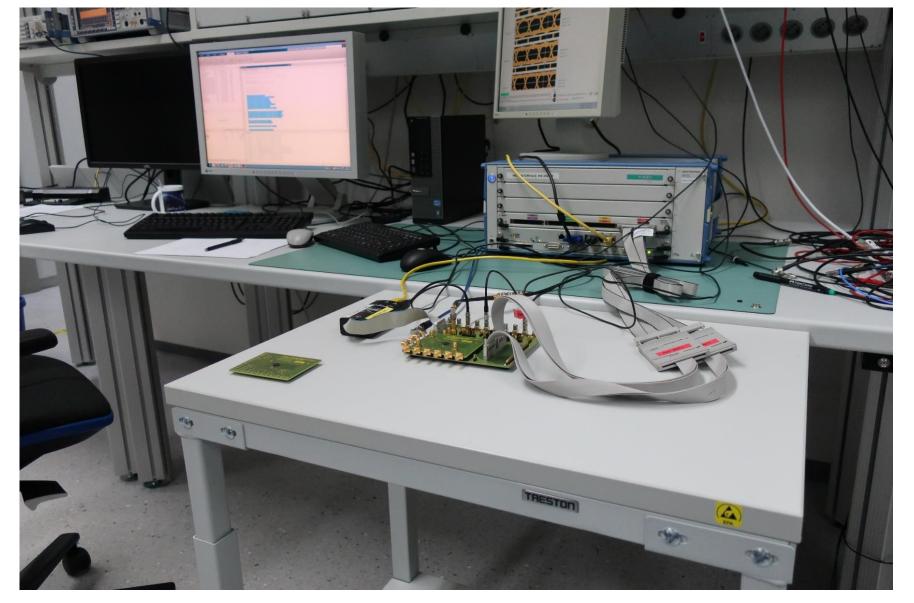

#### LAB SETUP OVERVIEW

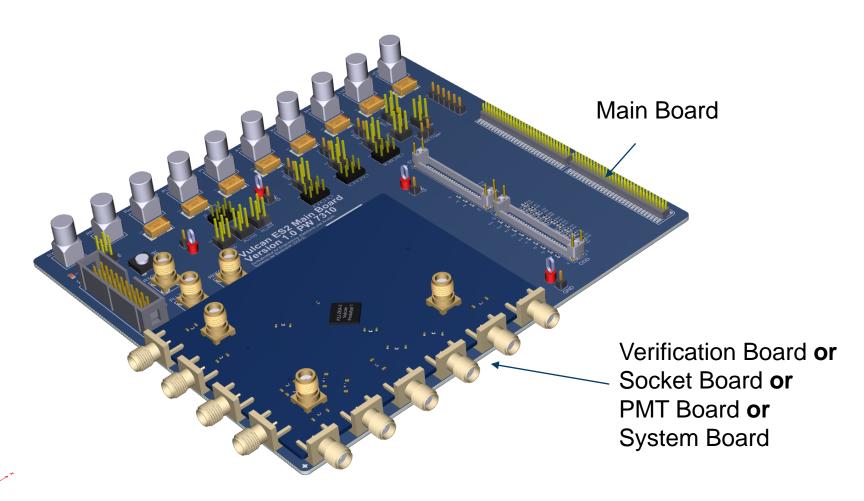

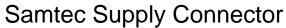

#### **BOARD CONCEPT**

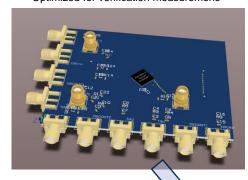

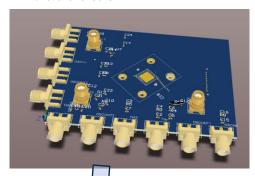

#### Verification Board

- Board for IC Verification

- Every ADC can be measured

- Best RF/Impedance performance

- Optimized for verification measuremens

#### Socket Board

- Socket can be populated on board

- For measurement of many samples

- Limited performance measurements

- Functional checks

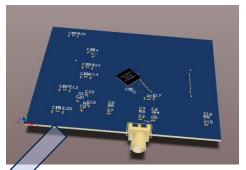

#### PMT Board

- For direct usage with PMT

- Protection circuit

- All 3 ADCs connected

#### System Board

- All 3 ADCs connected

- Protection circuit

- Reference design for system implementation

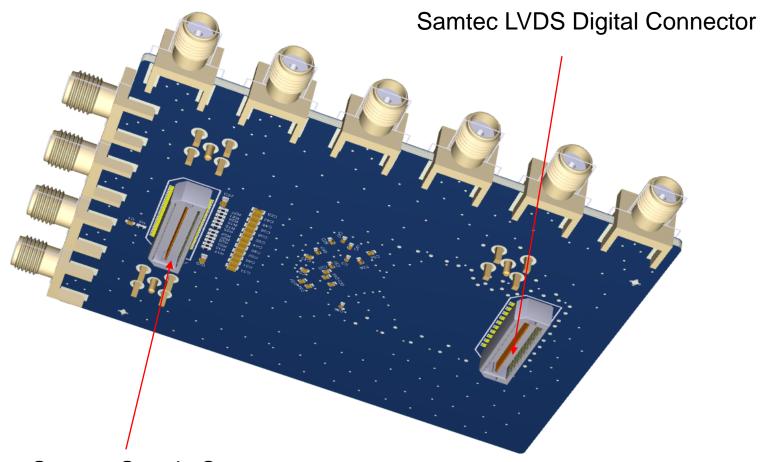

#### Main Board

- Logic analyser connection

- Power supply connection

- JTAG interface

- DC measurements

- Samtec board to board connectors

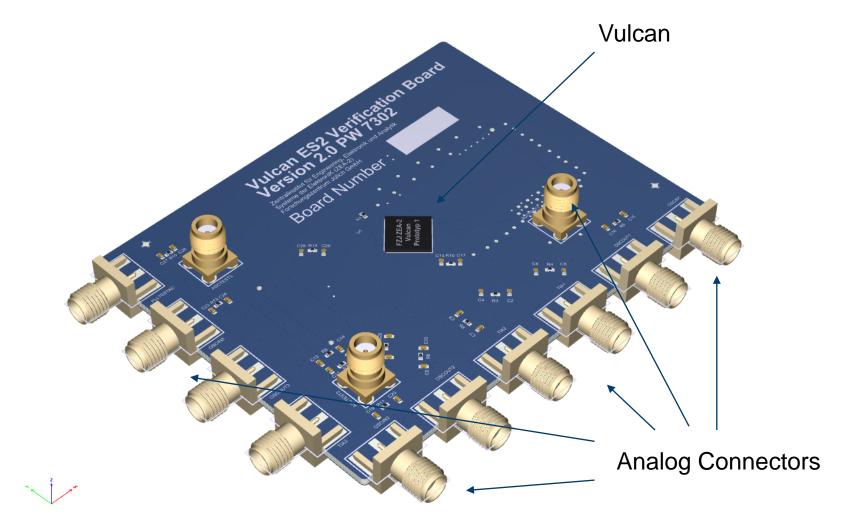

#### **VERIFICATION BOARD CONCEPT**

#### **VERIFICATION BOARD**

#### **VERIFICATION BOARD**

#### VERIFICATION BOARD SETUP

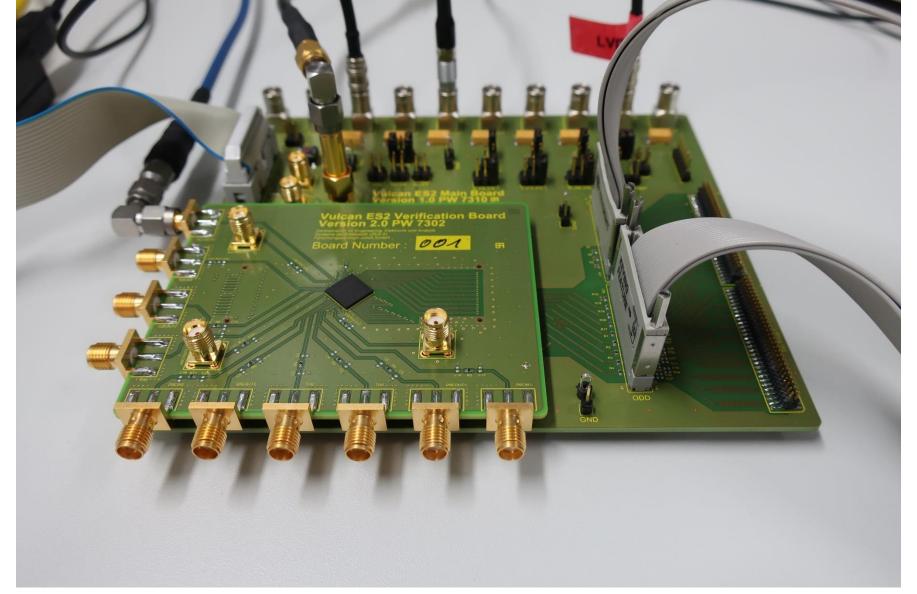

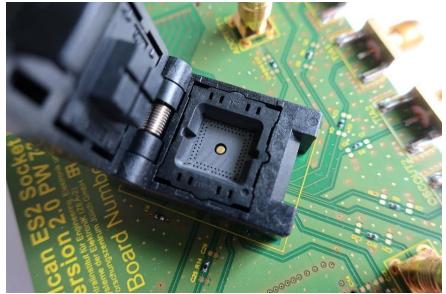

#### **SOCKET BOARD SETUP**

Yamaichi Socket for functional testing

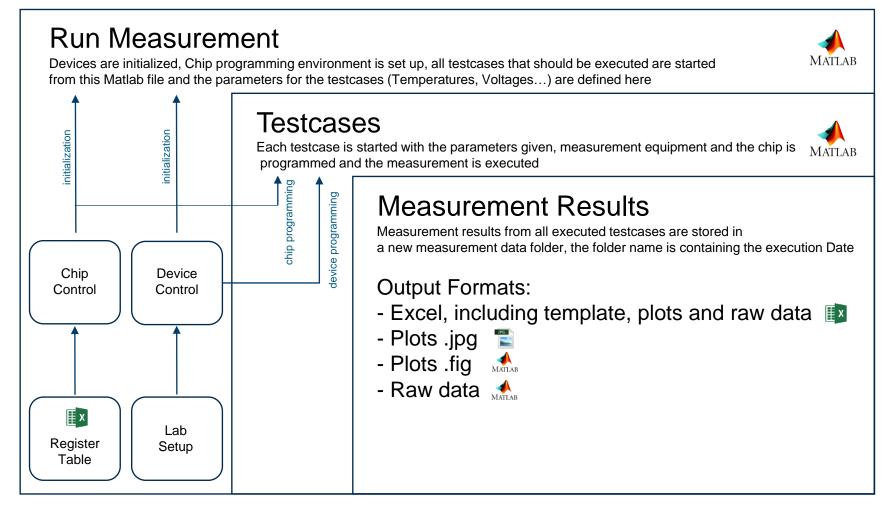

#### **VERIFICATION SOFTWARE FRAMEWORK**

#### **VERIFICATION RESULTS OF VULCAN ES2**

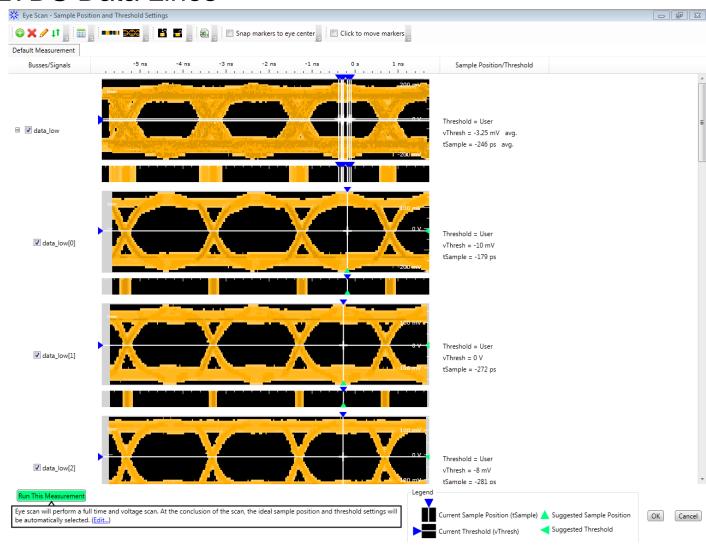

• LVDS Data Lines

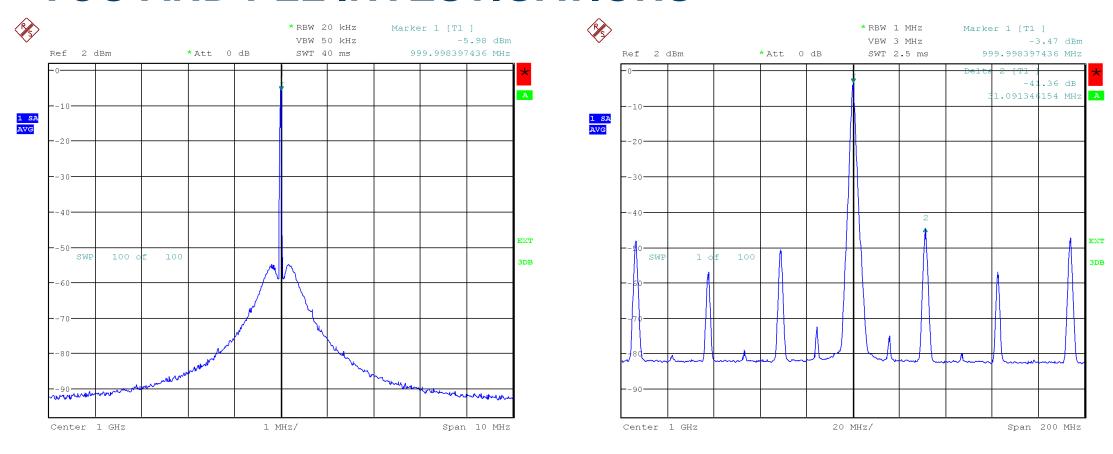

#### **VCO AND PLL INVESTIGATIONS**

Date: 15.DEC.2003 07:15:24

Date: 15.DEC.2003 07:17:58

- VCO running @4GHz

- Reference clock for PLL @31.25MHz

- Measurement VCO/4 -> 1GHz

#### **CLOCK AND PLL INVESTIGATIONS**

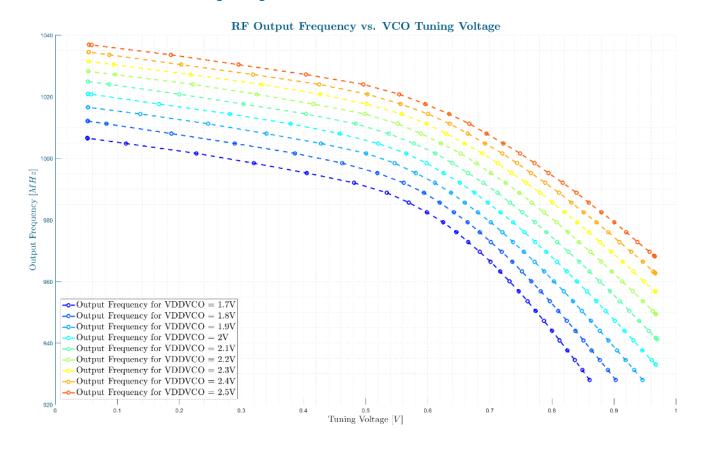

VCO Tuning Range @ 25°C

#### • PLL Phase Noise @ 25°C

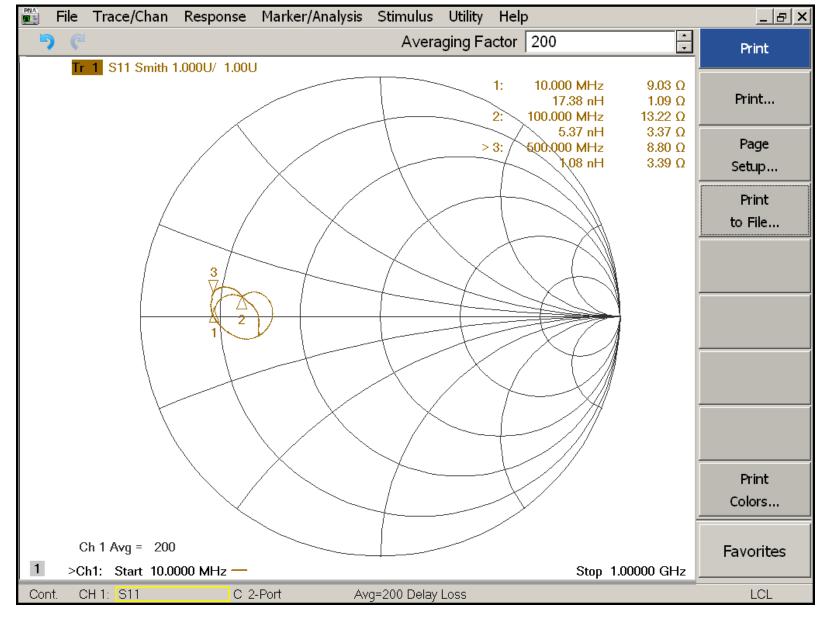

# TRANSIMPEDANCE AMPLIFIER INPUT IMPEDANCE

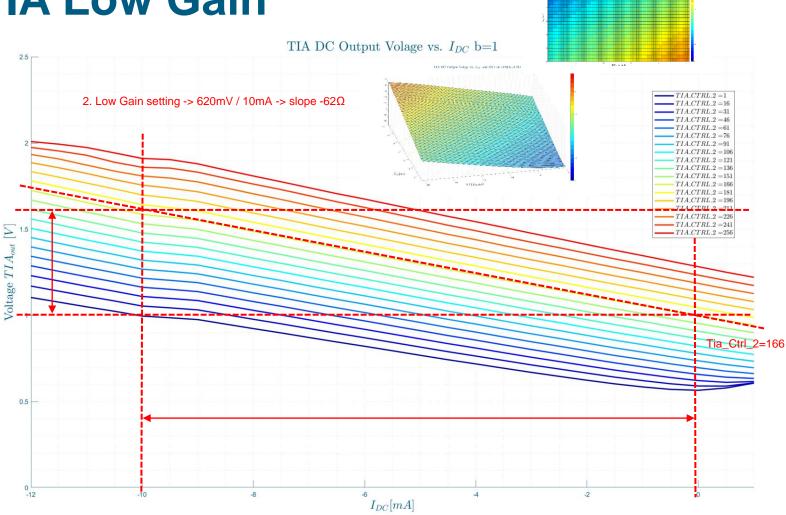

#### **TIA Low Gain**

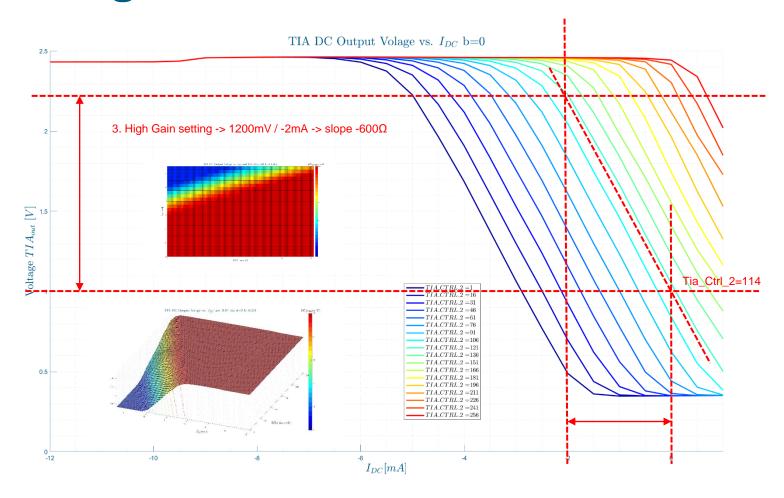

#### **TIA High Gain**

-2000 Current [uA]

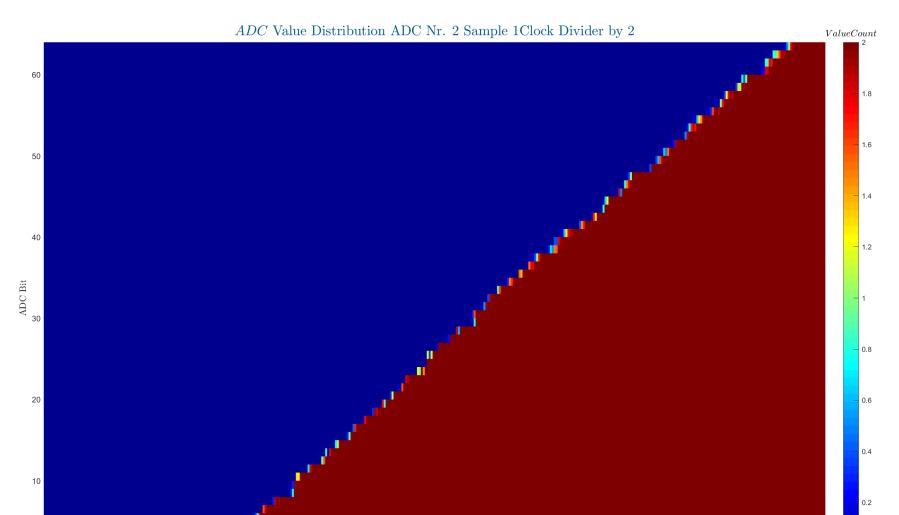

# ADC Thermometer Code Distribution 500Msample/s

-500

-1000

-3000

-2500

-1500

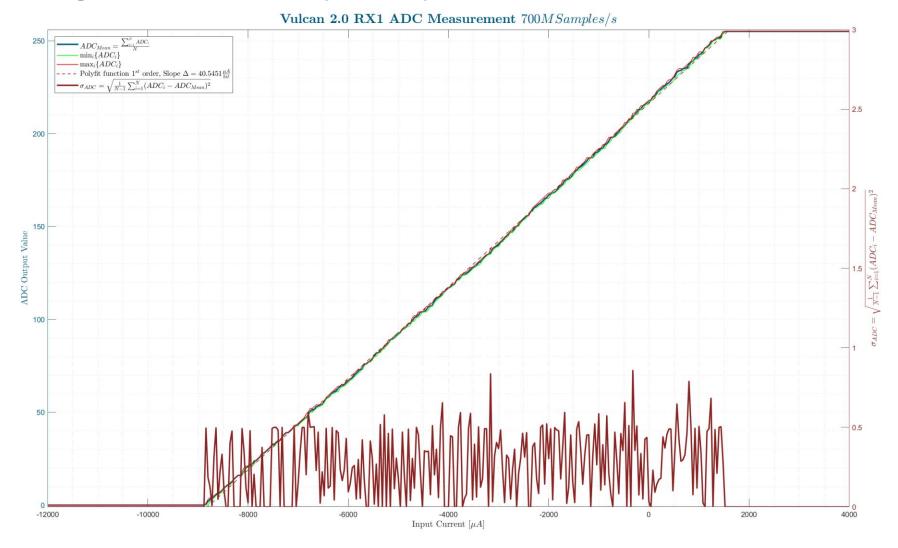

#### **Full Range ADC Characteristic (low Gain)**

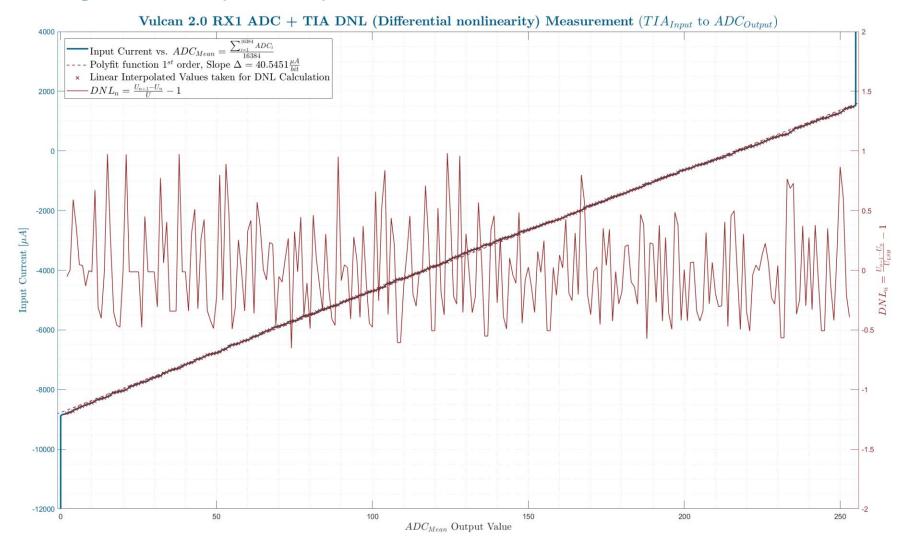

#### **Full Range ADC DNL (low Gain)**

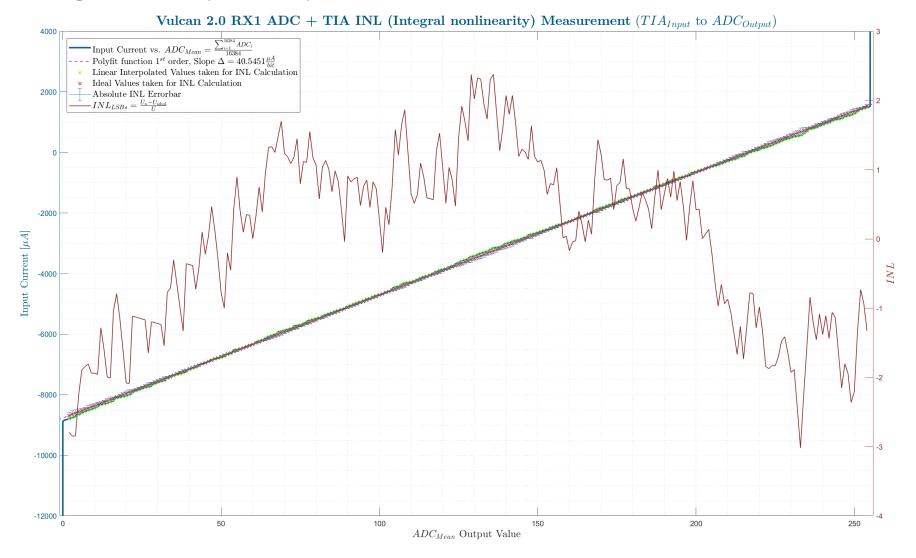

#### **Full Range ADC INL (low Gain)**

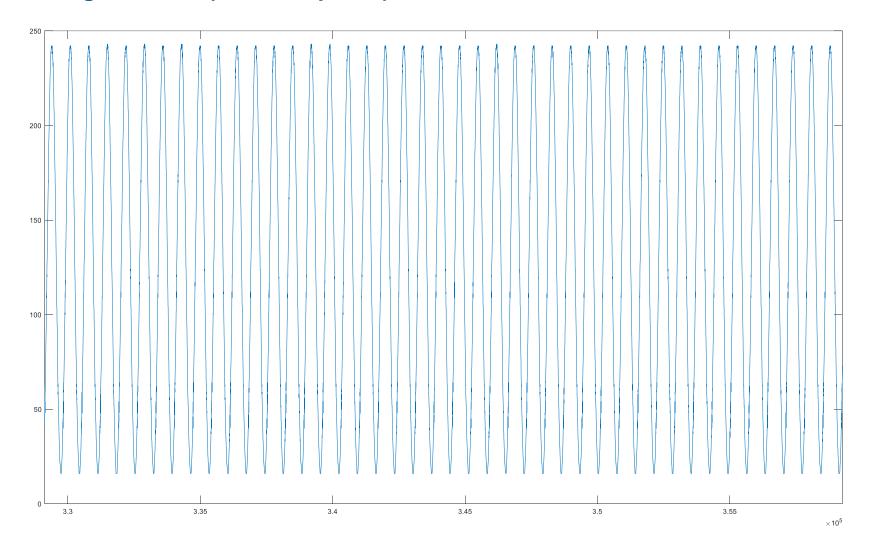

#### Sinewave Signal 1 MHz (700Msamples/s)

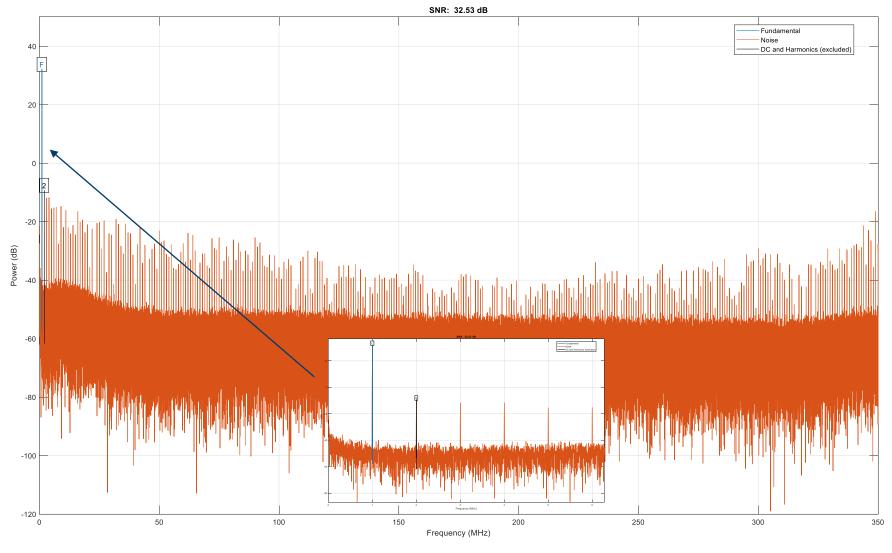

#### **SNR Measurement (700Msamples/s)**

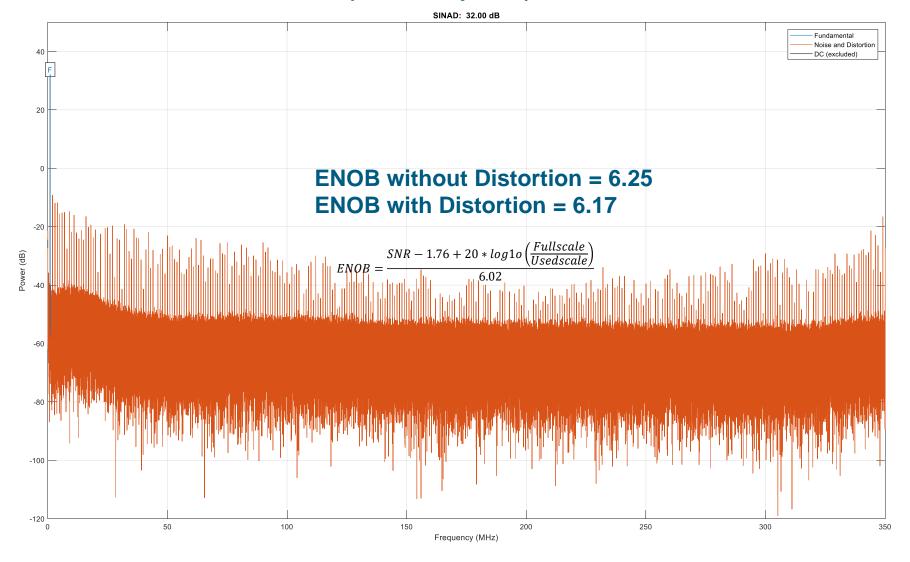

#### **SNR Measurement with Distortion (700MSamples/s)**

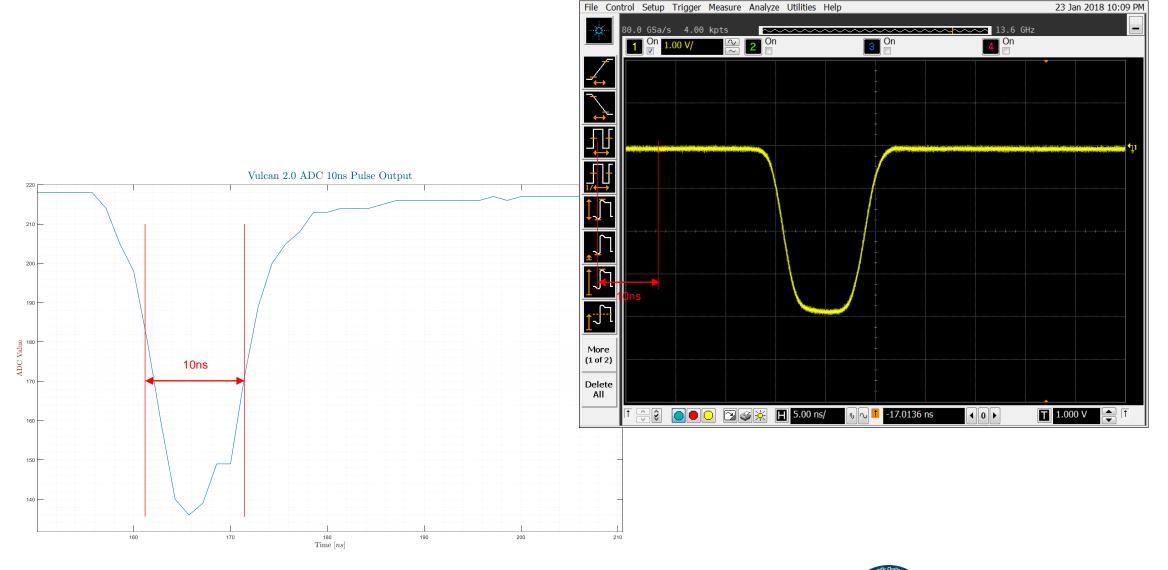

#### **10ns Pulse ADC Output**

### Vielen Dank!